Sekančius EPYC procesorius gali sudaryti devyni lustai

Apie būsimus EPYC procesorius, turinčius „Rome“ kodinį pavadinimą, atsiranda vis naujos informacijos. Pirmasis kelių lustų idėją EPYC procesoriuose iškėlė „AdoredTV“ kanalas, o dabar ši tema toliau gvildenama „Twitter“ pranešime, kurį parašė buvęs inžinierius.

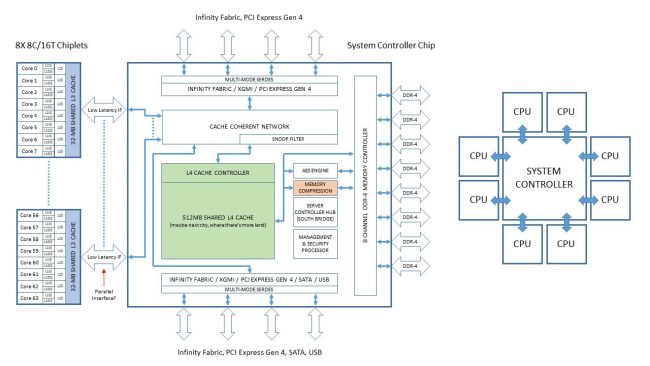

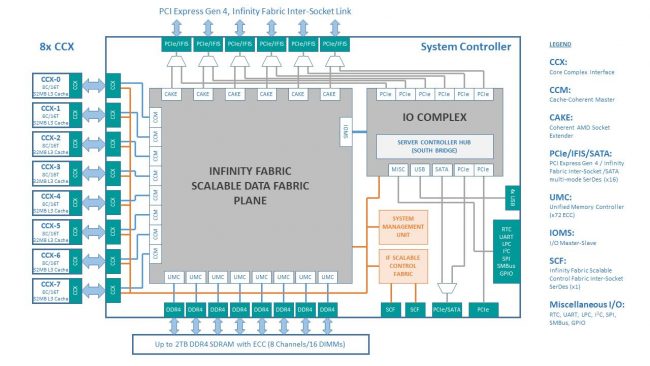

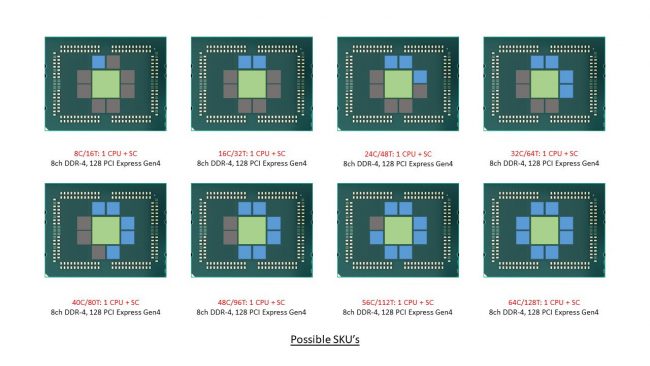

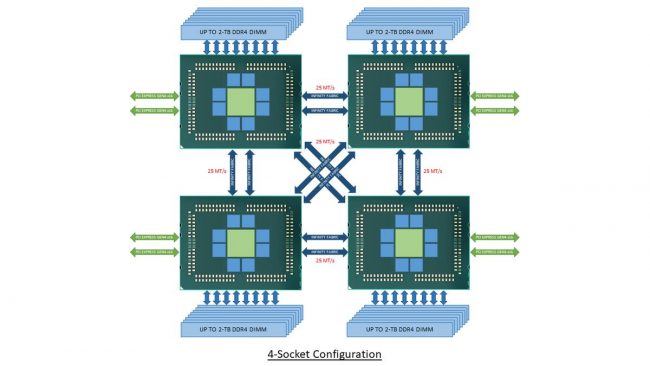

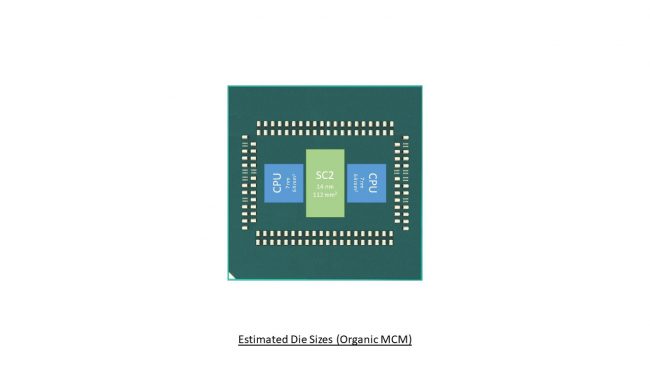

Dabartiniai EPYC procesoriai gali kentėti nuo blogo atminties pasiekiamumo, kas tam tikrose scenarijuose priveda prie spartos praradimo. Duomenų pralaidumas serveriuose labai svarbu, tad AMD galimai keičia savo dizainą į kelių lustų. Iš tikro jų būtų net 9: 8 lustai būtų procesoriaus branduoliai, o devintas viską jungiantis sistemos kontrolerio lustas. Lustuose būtų po 8 branduolius. Šie lustai turėtų išjungtą šiaurinį tiltą, kurio pagalba pasiekiama atmintis. Vietoj to atminties operacijas vykdytų sisteminis kontroleris, kuris galėtų būti jungiamas prie 8 kanalų ir palaikyti iki 2 TB ECC atminties. Sistemos kontroleris dar turėtų 96 PCIe 4.0 linijas, tai leistų pajungti 6 vaizdo plokštes naudojant x16 pralaidumą arba 12 vaizdo plokščių naudojant x8 pralaidumą. Šiame sistemos kontroleryje būtų ir pietinis tiltas su SATA, USB ir kitomis I/O jungtimis. Norint pagerinti pietinio tilto funkcionalumą galėtų būti naudojamas ir atskiras išorinis lustas.

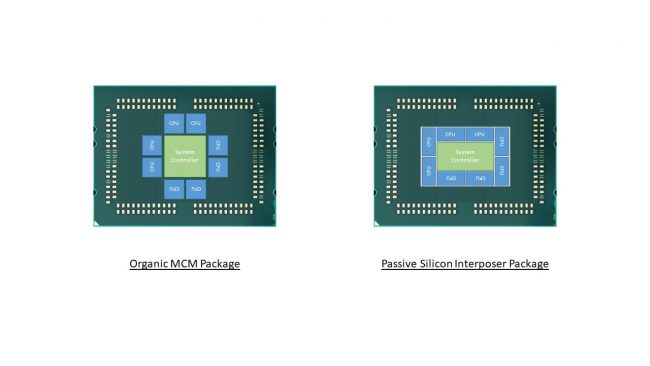

Visi šie lustai būtų pasodinami ant silicio pagrindo, panašiai kaip daroma su „Vega“ vaizdo plokštėmis ir HBM atmintimi.

Reikia suprasti, kad informacija nėra oficiali, bet iš kelių šaltinių girdint panašius gandus galima jais ir patikėti.

Idomu koks bus latency tarp serdziu. Taip pat, ar i mainstream des 2 x 8C ar 1. Galetu jau prasideti gandu sezonas apie ZEN2 – nelabai kas idomaus buvo pastaruoju metu 🙂

panikuoja ar nepanikuoja?

„kernel_panikuoja“ senas acc, kuri buvau specialiai uzsiblokaves, nes norejau padaryt pertrauka gincuose del nesamoniu 🙂

kad jau atsiblokavai, tai kaip tau naujasis 9900k? pateisino lukescius?

Gal norėčiau Z390 testavimams 9900K pasiimt, bet net iš skelbimų pigiau už 600 nekyla ranka imti…

O kernel šaunuolis, kad nebesipriešina savo pašaukimui 🙂

Su juo viskas gerai, isskyrus kaina. Kainuotu 350EUR kaip 2700X, visi nestu tasem juos 😀 Deja, jis kainuoja virs 700EUR dabar (tiksliau numatoma, ju net nera LT). As asmeniskai buvau nusiteikes uz ji moketi max iki 500EUR, bet nei cento daugiau. Aisku cia dar Intel shortage’as i visa tai isipaise, bet net ir be jo 9900K butu apie 600EUR pas mus.

Jei lapkritį atskleidimas, tai greitai ir prasidės 🙂

https://www.techpowerup.com/249151/amds-zen-2-could-be-revealed-on-november-6th-next-horizon-event-scheduled

Labai jau greitai būtų, aš tiesiog aptakių frazių laukiu. Nesitiki, kad 7nm jau paruošti tuoj tuoj procesorius paleidinėti, net ir mažais kiekiais.