„Zen 3“ architektūra nebeturės CCX dizaino

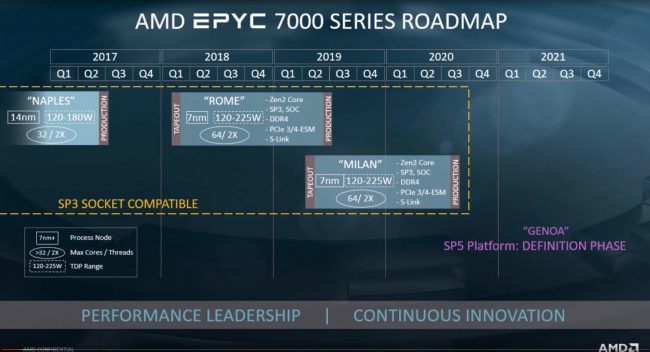

AMD visai neseniai išleido „Zen 2“ architektūros procesorius, o mes vis dažniau girdime apie „Zen 3“ naujoves. Būsimi „Zen 3“ architektūros lustai bus gaminami naudojant 7 nm EUV patobulintą litografiją ir vien jau tai turi pridėti papildomos spartos, bet AMD ruošia ir daugiau staigmenų.

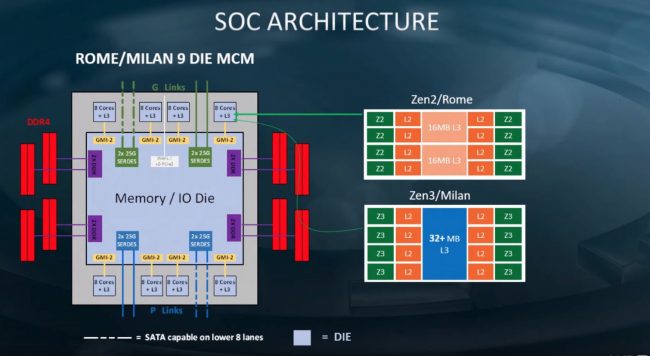

Dabar vienas 8 branduolių procesoriaus lustas turi du CCX blokus. Kiekviename jų yra 4 branduoliai ir 16 MB L3 spartinančiosios atminties. Su „Zen 3“ panašus lustas nebeturės dviejų CCX, o vietoj jo luste bus 8 branduoliai ir bendra 32 MB L3 spartinančioji atmintis. Tai iš karto turi pagerinti bendravimą tarp branduolių, nes dabar norint susikalbėti dviem branduoliams iš skirtingų CCX, prarandama sparta. Toks naujas dizainas supaprastins lustų dizainą, o taip pat padidins kiekvienam branduoliui prieinamą L3 atminties kiekį.

Reikia paminėti, kad matomos skaidrės buvo paskelbtos AMD darbuotojo Mark Papermaster, bet po to jos buvo ištrintos. Iš Mark Papermaster pasisakymo dar sužinojome, kad „Zen 3“ taip pat siūlys dvigubai daugiau gijų vienam branduoliui. Tai reiškia, kad vienas „Zen 3“ branduolys turės 4 gijas. Šią informaciją buvome girdėję ir seniau. Pirmiausia „Zen 3“ turi pasirodyti EPYC procesoriuose ir tai turi įvykti 2020 metų trečiame ketvirtyje. Kada sulauksime staliniams kompiuteriams skirtų „Zen 3“ procesorių dabar nėra žinoma.

„Tai reiškia, kad vienas „Zen 3“ branduolys turės 4 gijas“.

Šitie gandai nepasitvirtino. Paskutinėje skaidrėje apačioje kairėje matyti.

https://youtu.be/2MSj9_dvjB4?t=66

mane tai sitas labiau liudina: https://prnt.sc/pfw9rd

Nu realiai AMD negali kaltinti, nes nei Micron, Hynix, Samsung nepristatė ddr5. Geriausiu atveju tik ‘Genoa’ galės palaikyti. AMD bent prastūmė Pci.e 4.0 standartą.

Šiaip jau anksčiau buvo sakė, kad amd zen 3 nebus DDR5, nes reiktu pakeisti architektūrą.

Zen3 manau praleisiu, lauksiu ZEN3+