„AMD Excavator“ architektūra leis pasiekti spartos persilaužimą?

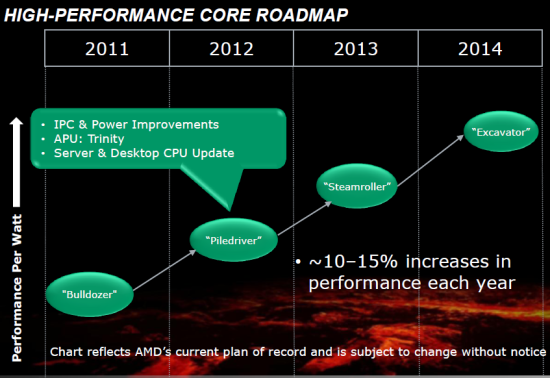

Nors AMD ir yra pareiškiusi pasitraukianti iš itin aukštos spartos centrinių procesorių kūrimo, daugelis konkurencijos aukščiausiame sektoriuje pasiilgusių vartotojų tikisi nemažo spartos proveržio kartu su sekančios kartos „Steamroller“ architektūra. Entuziastai net pažėrė keletą spėjimų (gandų lygio informacijos) apie „Excavator“ branduolius, kurie turėtų turėti didžiulių pakitimų dėl naujai integruoto instrukcijų apdorojimo bloko.

Neseniai GCC bendruomenei pristatytas ir tik bendro lygio „Excavator“ architektūros palaikymą „Linux“ terpėje įgalinantis paketas gali atskleisti keletą paslapčių, kurias turės naujieji AMD procesoriai. Remiantis iš AMD atitekėjusia informacija, „Excavator“ palaikys SSE4.1, SSE4.2, AES, PCLMUL, AVX, BMI, F16C, MOVBE, AVX2, BMI2, RDRND bei kitas instrukcijas. Ateities aplikacijoms, žinoma, svarbiausii, tampa AVX2, kuris įdiegtas į „Intel Haswell“ procesorius.

Šių instrukcijų implementacija reikalauja kardinalaus aparatinės įrangos pertvarkymo. Dabartinis „Bulldozer“ architektūros slankiojančio kablelio blokas geba susitvarkyti tik su 128 bitų sveikųjų skaičių operacijomis, tuo tarpu AVX2 galimybės praplatėja iki 256 bitų SIMD instrukcijų. Nenuostabu, kad AMD reikalingas kardinaliai atnaujintas arba net nuo nulio surinktas slankiojančio kablelio blokas, kuris yra dalinamasis tarp dviejų aritmetinių/loginių blokų dabartiniame „Bulldozer“ modulyje.

Tokie pakitimai 2015-2016 metais turėtų leisti pasiekti dramatišką spartos proveržį didžiojoje dalyje pažangių aplikacijų. Visgi atrodo, kad „Intel“ nežada pasiduodi instrukcijų kare, mat „Skylake“ architektūros procesoriai jau turės AVX 3.2 paketą, kuris dirba su 512 bitų instrukcijomis.

Naujausi komentarai